If you need the SATA project source code, please contact me. The code requires payment.

WeChat ID: yesfpga

1:FPGA SATA IP

The characteristics of the FPGA based SATA host controller are as follows:

1. Supports SATA 1 (1.5Gbps), SATA 2 (3Gbps), and SATA 3 (6Gbps)

2. Complies with SATA Rev 3.0 specifications

3. Implements the Phy Layer protocol, including OOB, etc.

4. Implements the Link Layer protocol, including 8B/10B encoding and decoding, scrambling, CRC, flow control, framing/ deframing, communication handshake sequences, etc.

5. Implements the Transport Layer protocol, including FIS construction and parsing, error retransmission mechanisms, etc.

6. Implements the Command Layer protocol, including Software Reset protocol, PIO Data-In protocol, PIO Data-Out protocol, DMA-In protocol, DMA-Out protocol, etc.

7. Implements the Application Layer protocol, including device self-check, executing IDENTIFY DEVICE command (to obtain device parameters), DATA SET MANAGEMENT command (Trim), and DMA controller

8. Implements hot-swappable SATA

9. By using multiple SATA Host Controllers, a RAID array controller can be constructed

The interface characteristics of the FPGA based SATA host controller are as follows:

1. Supports 1.5Gbps, 3Gbps, 6Gbps line rates

2. Provides FIFO data stream interface, supports flat address access (only need to provide the starting sector address and total sector length, the controller has a built-in DMA controller to achieve continuous sector address management access), enabling high-throughput data read and write

3. Provides a dual-port RAM interface, supports single sector address access, enabling 512-byte data read and write

4. Provides a dual-port RAM interface, supports 1~16 sector address access, enabling up to 8192-byte data read and write

5. Provides a dual-port RAM interface, supports 1~16 512-byte blocks (LBA Range Entry list), enabling Trim functionality

6. Provides SATA Host register interface, including status and error register output

7. Provides device self-check status output, device parameter output (such as maximum available sector count), Trim support has been tested and validated on multiple SSDs (Intel, Samsung, Micron, OCZ, Kingston, Sandisk, etc.), the controller’s performance is as follows:

1. SATA 2 interface, continuous write speed greater than 230MB/s, continuous read speed greater than 250MB/s.

2. SATA 3 interface, continuous write speed greater than 520MB/s, continuous read speed greater than 540MB/s

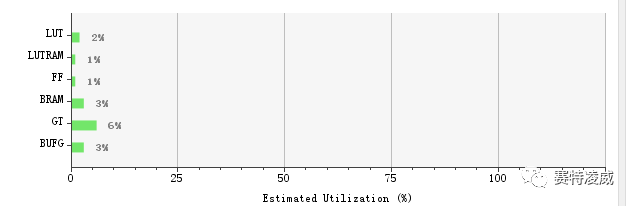

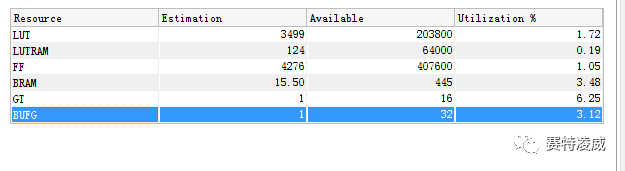

SATA IP resource consumption on K7 325T is as follows:

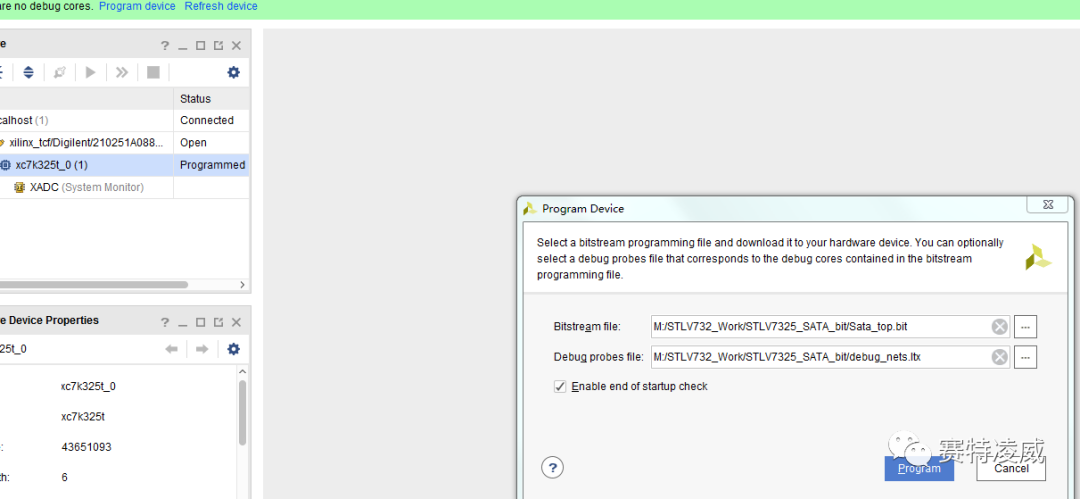

Download Sata_top.bit file and debug_nets.ltx file

|

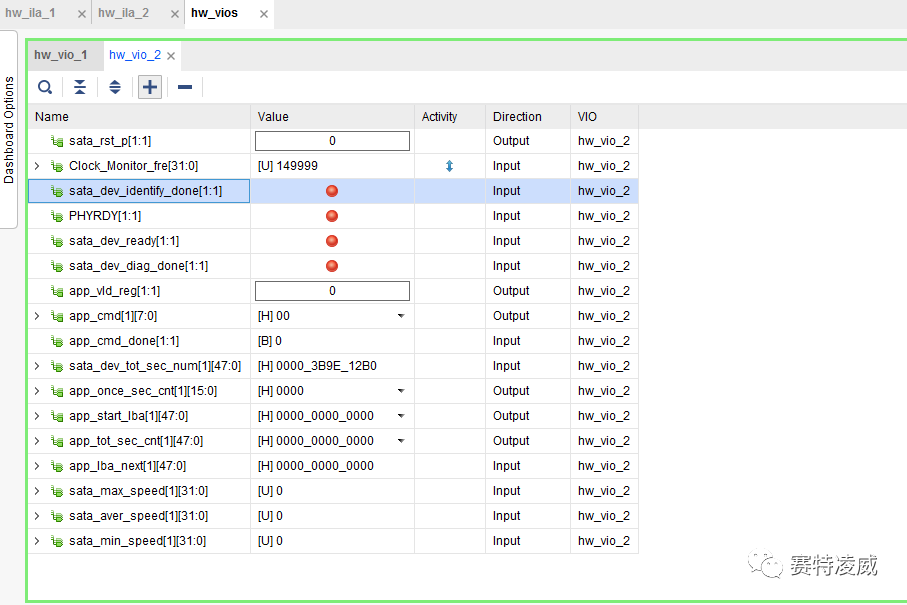

sata_rst_p |

Global reset, active high Set VIO to Active-high Button |

|

PHYRDY |

SATA physical layer signal, active high. If this signal is high, it indicates that the Phy has completed the OOB operation. |

|

sata_dev_diag_done |

SATA device self-check success signal, active high. |

|

sata_dev_identify_done |

SATA device self-check success signal, active high. |

|

sata_dev_ready |

SATA device self-check, active high. |

|

app_vld_reg |

Command enable signal, a high pulse Set VIO to Active-high Button |

|

app_cmd |

SATA read/write command, 0x10 is write, 0x20 is read |

|

app_cmd_done |

Read/write execution completion signal, active high |

|

sata_dev_tot_sec_num |

SATA disk capacity, in sectors |

|

app_once_sec_cnt |

Length of DMA read/writeSATA disk at once, in sectors Set VIO to unsigned |

|

app_start_lba |

SATA disk read/write, starting address, in sectors |

|

app_tot_sec_cnt |

Requested read/writeSATA disk capacity, in sectors |

|

app_lba_next |

Indicates the current read/writeSATA disk address, in sectors |

|

sata_max_speed |

TestSATA disk maximum speed, in MB/s Set VIO to unsigned |

|

sata_min_speed |

TestSATA disk minimum speed, in MB/s Set VIO to unsigned |

|

sata_aver_speed |

TestSATA disk average speed, in MB/s Set VIO to unsigned |

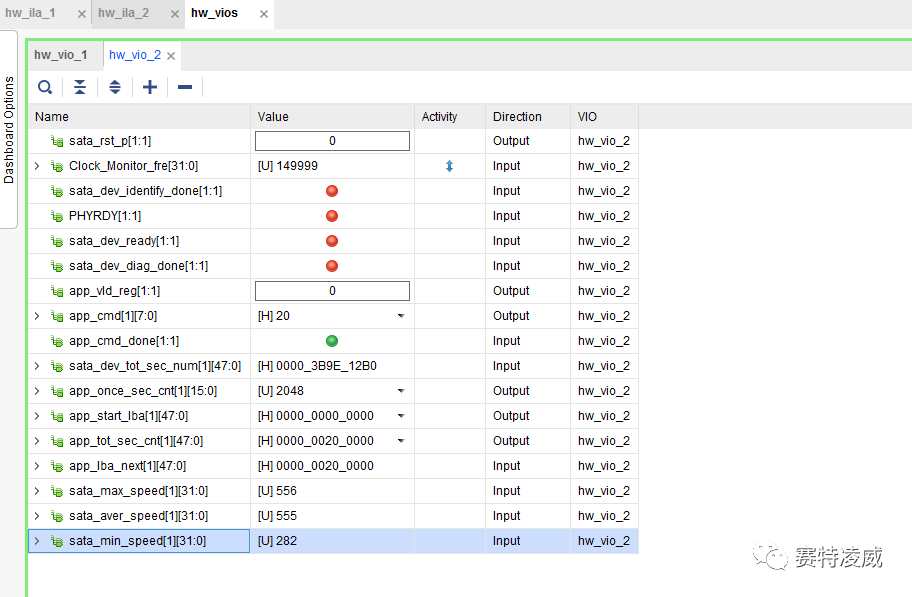

hw_vio signal virtual control

hw_vio_1 signal corresponds to SATA_A interface

hw_vio_2 signal corresponds to SATA_B interface

sata_dev_tot_sec_num[47:0] represents SATA solid-state drive total sector count, this example uses Samsung 860 PRO series;

Total capacity=0x3B9E12B0*512/1024/1024/1024=476.93GB

Each time you open VIO, you need to re-enter the value, otherwise Vivado will not write the vio value into the program.

3:Data Flow Testing

Request different app_tot_sec_cnt capacities, speeds vary, this is related to the SATA disk

1. DMA write test (SATA deviceà FPGA)

For example: Command(app_cmd) set to 0x10

Single data transfer length(app_once_sec_cnt) set to 2048, which is 1MB

Total length(app_tot_sec_cnt) set to0x000000200000, which is 1GB

2. DMA read test (SATA deviceà FPGA)

For example: Command(app_cmd) set to 0x20.

Single data transfer length(app_once_sec_cnt) set to 2048,

Total length(app_tot_sec_cnt) set to0x000000200000,

|

Write test 860 PRO capacity |

Maximum speed |

Minimum speed |

Average |

|

1GB |

522 |

277 |

521 |

|

10GB |

522 |

290 |

521 |

|

Full disk 470GB |

522 |

280 |

521 |

|

Read test 860 PRO capacity |

Maximum speed |

Minimum speed |

Average |

|

1GB |

556 |

282 |

555 |

|

10GB |

556 |

291 |

555 |

|

Full disk 470GB |

556 |

290 |

556 |

For current SATA disks, it is common to experience speed drops; Samsung 860 Pro is a high-end SATA disk that does not drop speed; different SATA disks have different speeds, with typical SATA disks on the market having write speeds around 300MB.